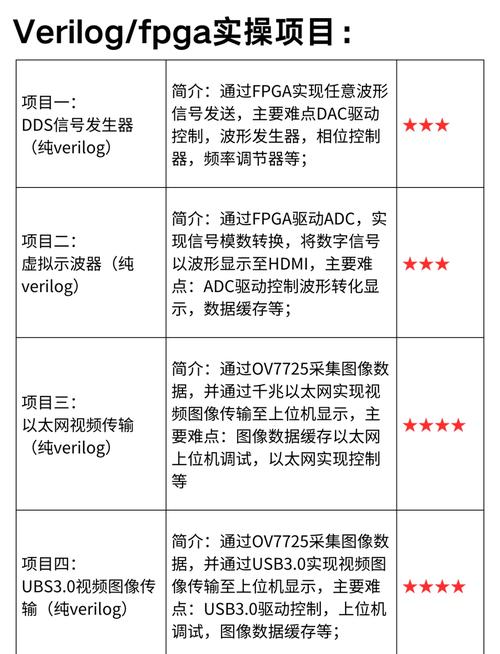

verilog除法器,深入探讨Verilog中的除法器完成

时间:2024-12-19阅读数:15

在Verilog中,完成除法器有多种办法,首要取决于所需的精度、速度和资源利用率。下面是一个简略的定点除法器的示例,运用移位和减法操作来完成。

```verilogmodule divider dividend, input divisor, output reg quotient, output reg remainder, output reg doneqwe2;

reg temp_dividend; reg temp_divisor; reg temp_quotient; reg temp_remainder; reg count;

always @ begin if begin // Asynchronous reset temp_dividend endmodule```

这个除法器是一个串行除法器,它在一个时钟周期内进行一次减法操作。它将除数和被除数左移,直到除数大于被除数,然后进行减法,并将商的一位设置为1。这个进程重复进行,直到被除数小于除数。商和余数存储在`temp_quotient`和`temp_remainder`中,并在核算完成后输出。

深入探讨Verilog中的除法器完成

在数字体系规划中,除法器是一个重要的组成部分,尤其在需求准确核算和操控的场合。Verilog作为一种硬件描绘言语(HDL),在FPGA和ASIC规划中得到了广泛使用。本文将深入探讨Verilog中除法器的完成办法,包含其基本原理、规划过程以及在实践使用中的留意事项。

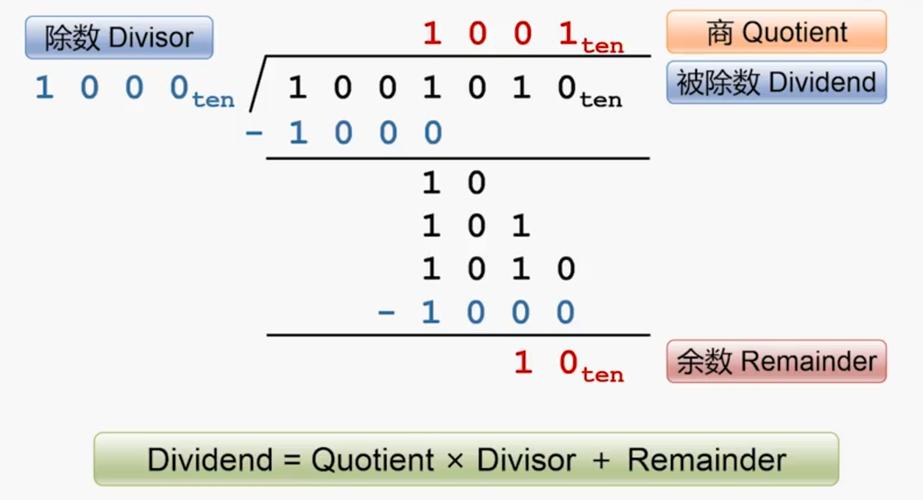

一、除法器的基本原理

除法器的基本功能是将一个数(被除数)除以另一个数(除数),得到一个整数(商)和一个余数。在Verilog中,除法器的完成一般依据以下两种算法:

依据减法的除法器

依据乘法的除法器

二、依据减法的除法器完成

依据减法的除法器经过不断减去除数,直到被除数小于除数停止,记载减去除数的次数,即为商。以下是依据减法的除法器Verilog代码示例:

```verilog

module divider(

input [31:0] dividend,

input [31:0] divisor,

input clk,

output reg [31:0] quotient,

output reg [31:0] remainder

reg [31:0] temp_dividend;

reg [31:0] temp_divisor;

reg [31:0] count;

always @(posedge clk) begin

if (divisor != 0) begin

temp_dividend = temp_divisor) begin

temp_dividend 依据乘法的除法器经过不断乘以一个挨近1的数,逐步迫临被除数,直到乘积大于或等于被除数停止,记载乘数的倒数,即为商。以下是依据乘法的除法器Verilog代码示例:

```verilog

module divider(

input [31:0] dividend,

input [31:0] divisor,

input clk,

output reg [31:0] quotient,

output reg [31:0] remainder

reg [31:0] temp_dividend;

reg [31:0] temp_divisor;

reg [31:0] count;

reg [31:0] multiplier;

always @(posedge clk) begin

if (divisor != 0) begin

temp_dividend = temp_divisor multiplier) begin

multiplier 在实践使用中,规划除法器时需求留意以下几点:

保证除数不为零,以防止除法运算过错。

依据实践需求挑选适宜的算法,以平衡资源耗费和运算速度。

考虑除法器的精度和规模,保证满意规划要求。

在FPGA规划中,留意时序束缚,防止规划中的时序问题。

Verilog中的除法器规划是数字体系规划中的一个重要环节。本文介绍了依据减法和依据乘法的除法器完成办法,并供给了相应的Verilog代码示例。在实践使用中,依据详细需求挑选适宜的算法,并留意相关留意事项,以保证除法器规划的正确性和可靠性。

本站所有图片均来自互联网,一切版权均归源网站或源作者所有。

如果侵犯了你的权益请来信告知我们删除。邮箱:[email protected]

猜你喜欢

-

耗费运用python编程,从根底到实践

运用Python编程一般触及以下几个进程:1.装置Python:首要,你需求保证你的核算机上装置了Python。你能够从Python官方网站下载并装置合适你操...

2025-01-10后端开发 -

r言语装置教程,R言语保姆级装置教程

装置R言语是一个相对简略的进程,以下是一个根本的装置攻略。请注意,具体的过程或许会根据您的操作体系和R版别的不同而有所差异。装置R言语1.下载R言语拜访R官方网站:https://www.rproject.org/在“DownloadR”部分,挑选合适您操作体系的版别...。

2025-01-10后端开发 -

java8,敞开高效编程新时代

Java8是Java编程言语的第八个首要版别,于2014年3月18日发布。这个版别引入了许多新的特性和改善,包含Lambda表达式、流...

2025-01-10后端开发 -

铃木swift报价,全面解析这款小型车的商场行情

依据我找到的信息,铃木Swift(在中国商场被称为“雨燕”)的最新报价如下:1.日本商场:新一代铃木Swift在日本供给1.2升燃油版和1.2升轻混版两种动力挑选,并依据装备不同分为XG(燃油版)、MX(轻混版)、MZ(轻混版)三种车型,价格区间为172.7万233.2万日元,约合人民币8...。

2025-01-10后端开发 -

swift怎样读,耗费开端学习Swift

Swift是一种编程言语,首要用于iOS、macOS、watchOS和tvOS的开发。它由苹果公司于2014年推出,旨在代替ObjectiveC...

2025-01-10后端开发