verilog异或,深化解析Verilog中的异或操作

时间:2025-01-09阅读数:4

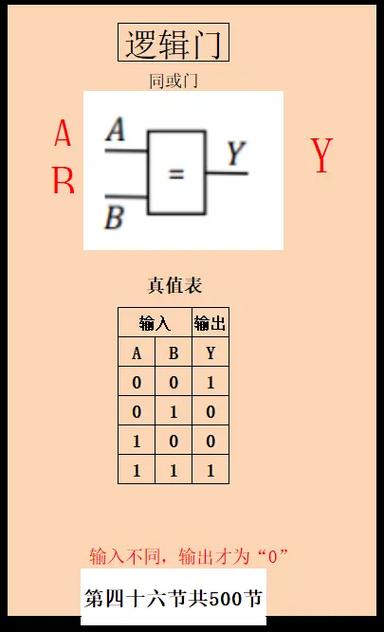

在Verilog中,异或运算能够经过运用`^`符号来完成。异或运算的成果是当两个输入位不一起为1,相一起为0。下面是一个简略的Verilog模块示例,展现了怎么运用异或运算:

```verilogmodule xor_example ;

assign y = a ^ b;

endmodule```

在这个比如中,`xor_example`模块有两个输入`a`和`b`,以及一个输出`y`。输出`y`是`a`和`b`的异或成果。当`a`和`b`的值不一起,`y`为1;当`a`和`b`的值相一起,`y`为0。

深化解析Verilog中的异或操作

在数字电路规划中,异或(XOR)操作是一种根本的逻辑运算,用于比较两个二进制位是否不同。Verilog作为一种硬件描绘言语,供给了丰厚的逻辑运算符来支撑这种操作。本文将深化探讨Verilog中的异或操作,包含其根本用法、完成方法以及在实践规划中的运用。

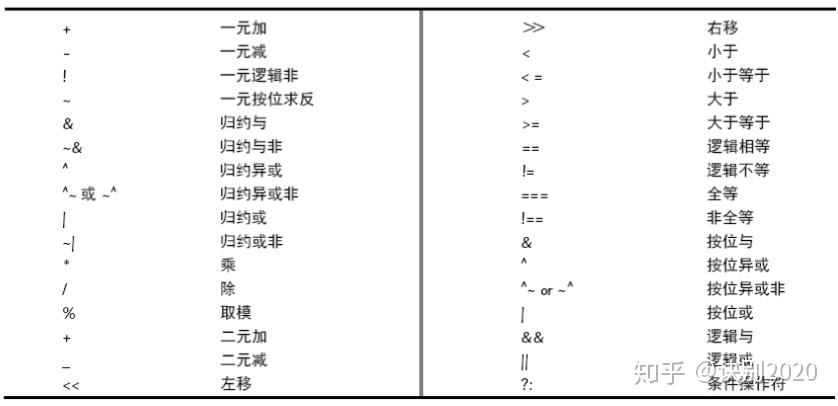

一、Verilog中的异或运算符

在Verilog中,异或运算符用符号“^”表明。它能够直接运用于两个二进制数,回来一个成果,该成果为1当且仅当两个输入位不同,否则为0。

二、异或运算符的语法

以下是一个简略的异或运算符的比如:

```verilog

module xor_example (

input a,

input b,

output y

assign y = a ^ b;

endmodule

在这个比如中,`a`和`b`是两个输入信号,`y`是输出信号。当`a`和`b`的值不同(一个为1,另一个为0)时,`y`的值将为1;假如它们相同,`y`的值将为0。

三、异或运算的完成方法

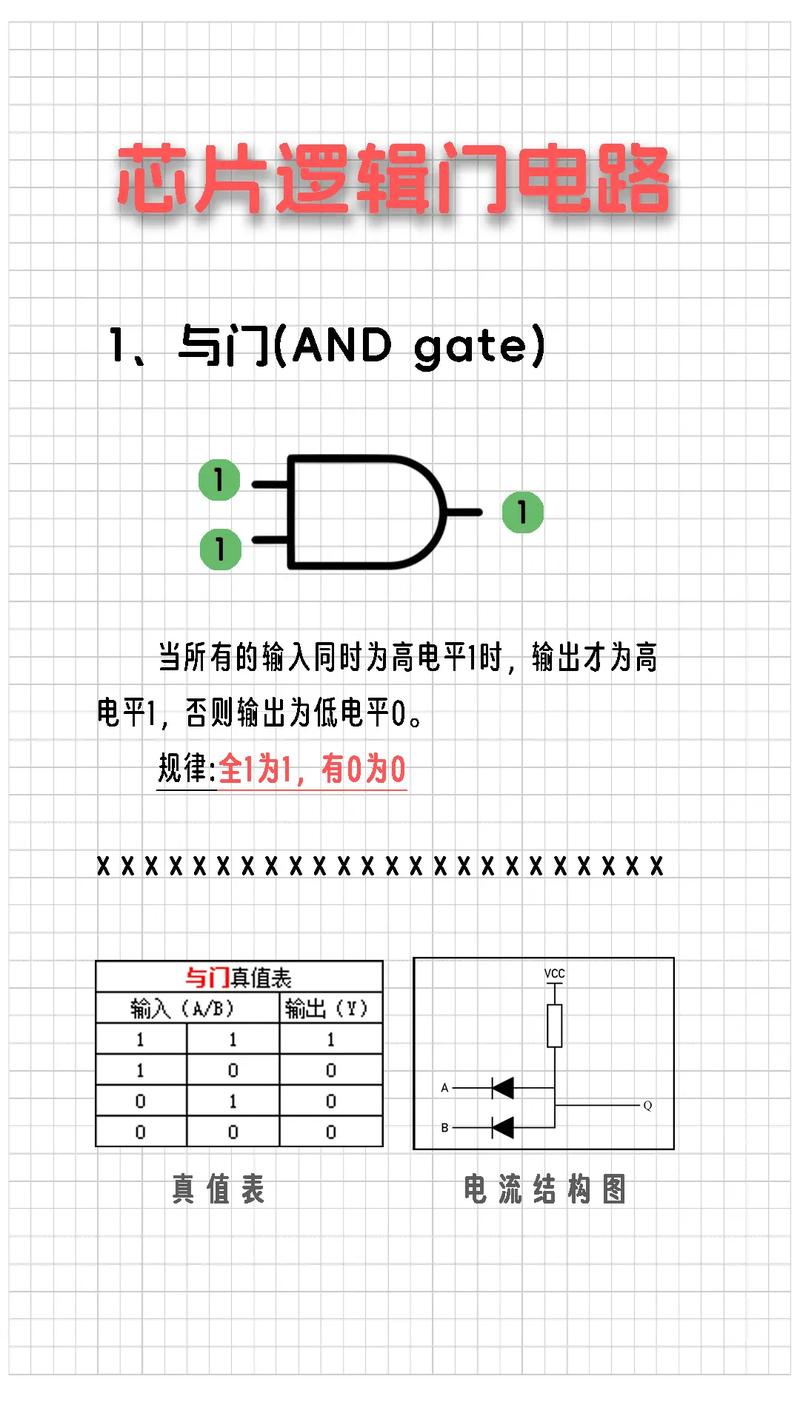

1. 逻辑门完成

异或运算能够经过两个与门(AND)和一个或门(OR)的组合来完成。以下是运用逻辑门完成的异或运算的Verilog代码:

```verilog

module xor_gate (

input a,

input b,

output y

wire w1, w2;

assign w1 = a

本站所有图片均来自互联网,一切版权均归源网站或源作者所有。

如果侵犯了你的权益请来信告知我们删除。邮箱:[email protected]

猜你喜欢

-

耗费运用python编程,从根底到实践

运用Python编程一般触及以下几个进程:1.装置Python:首要,你需求保证你的核算机上装置了Python。你能够从Python官方网站下载并装置合适你操...

2025-01-10后端开发 -

r言语装置教程,R言语保姆级装置教程

装置R言语是一个相对简略的进程,以下是一个根本的装置攻略。请注意,具体的过程或许会根据您的操作体系和R版别的不同而有所差异。装置R言语1.下载R言语拜访R官方网站:https://www.rproject.org/在“DownloadR”部分,挑选合适您操作体系的版别...。

2025-01-10后端开发 -

java8,敞开高效编程新时代

Java8是Java编程言语的第八个首要版别,于2014年3月18日发布。这个版别引入了许多新的特性和改善,包含Lambda表达式、流...

2025-01-10后端开发 -

铃木swift报价,全面解析这款小型车的商场行情

依据我找到的信息,铃木Swift(在中国商场被称为“雨燕”)的最新报价如下:1.日本商场:新一代铃木Swift在日本供给1.2升燃油版和1.2升轻混版两种动力挑选,并依据装备不同分为XG(燃油版)、MX(轻混版)、MZ(轻混版)三种车型,价格区间为172.7万233.2万日元,约合人民币8...。

2025-01-10后端开发 -

swift怎样读,耗费开端学习Swift

Swift是一种编程言语,首要用于iOS、macOS、watchOS和tvOS的开发。它由苹果公司于2014年推出,旨在代替ObjectiveC...

2025-01-10后端开发